The world of semiconductor technology has always been shrouded in a veil of complexity, but few things demystify it as effectively as a virtual teardown. Unlike physical dismantling, which risks damaging delicate components, virtual dissection allows engineers and enthusiasts alike to explore the intricate architecture of modern chips without ever touching a soldering iron. This approach has become indispensable in an era where transistors are measured in nanometers and a single chip can contain billions of them.

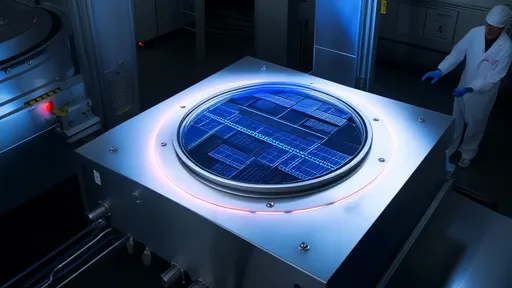

Virtual teardowns begin with advanced imaging techniques, typically using scanning electron microscopes or X-ray tomography to create high-resolution cross-sections of the chip. These images are then reconstructed into three-dimensional models that reveal layer upon layer of microscopic circuitry. What emerges is nothing short of technological artistry – a labyrinth of interconnects, logic gates, and memory cells arranged with precision that borders on the absurd. The latest processors from industry leaders like Intel, AMD, and Apple showcase designs so dense that if scaled to the size of a city, their wiring would make subway systems look simple by comparison.

One remarkable revelation from these virtual explorations is how much empty space exists within modern chips. Contrary to the packed silicon landscapes one might imagine, contemporary designs incorporate considerable void areas – not as flaws, but as carefully engineered thermal buffers and signal isolation channels. This spatial awareness at the nanoscale highlights how chip design has evolved from simply cramming in more transistors to orchestrating their harmonious operation. The virtual perspective makes these spatial relationships visible in ways that schematic diagrams never could.

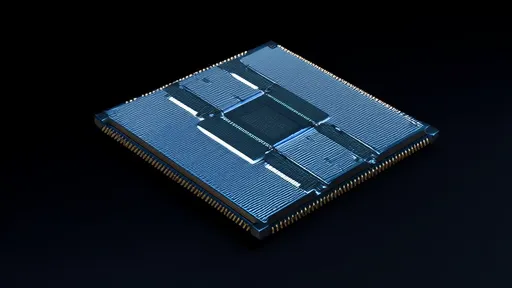

The memory hierarchy within processors proves particularly fascinating under virtual scrutiny. By peeling back layers, analysts can trace the physical implementation of cache structures, revealing how L1, L2, and L3 caches are positioned relative to processor cores. This spatial arrangement directly impacts latency and power consumption – factors that make or break processor performance. Recent teardowns of AMD's 3D V-Cache technology showed how stacking additional cache dies vertically can dramatically improve gaming performance, proving that in chip design, sometimes the best path forward is up.

Power delivery networks emerge as another star of the virtual teardown show. Modern chips require hundreds of amperes of current delivered at voltages sometimes below one volt, creating extraordinary challenges in power distribution. Virtual dissections reveal intricate mesh networks of power rails that resemble fractal patterns, designed to minimize voltage drops across the chip. The latest Intel and Apple silicon teardowns showcase increasingly sophisticated power delivery systems that help explain how today's chips achieve both high performance and remarkable energy efficiency.

Perhaps most surprisingly, virtual teardowns frequently uncover design choices that appear counterintuitive at first glance. Certain logic blocks might be placed far from components they interact with frequently, or cache structures might adopt seemingly irregular shapes. These quirks often reflect the complex trade-offs between thermal management, signal integrity, and manufacturing constraints that chip architects navigate. What looks like an oddity in a static image frequently makes perfect sense when considering the dynamic operation of the chip as a whole.

The security implications of virtual teardowns have sparked considerable debate in the industry. While these analyses help advance engineering knowledge, they also expose potential vulnerabilities in chip designs. Researchers have used virtual dissection techniques to identify security flaws like the infamous Spectre and Meltdown vulnerabilities before they were publicly disclosed. This dual-use aspect creates an ethical tightrope for those conducting and publishing such analyses, balancing transparency against the risk of empowering malicious actors.

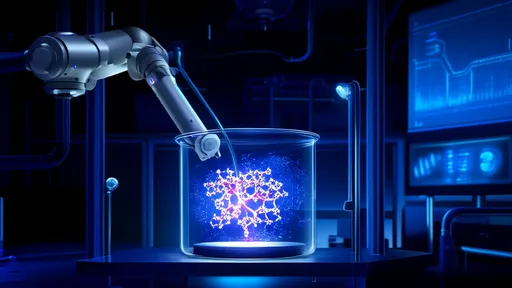

Looking ahead, virtual teardown technology continues to evolve alongside the chips it examines. Emerging techniques promise even higher resolution and the ability to analyze chips while they're operating, potentially revealing how circuits behave under different workloads. As quantum computing and photonic processors emerge on the horizon, these virtual dissection tools will face new challenges in visualizing radically different computing architectures. One thing remains certain: as long as chips grow more complex, engineers will find ever more ingenious ways to take them apart – if only virtually.

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025