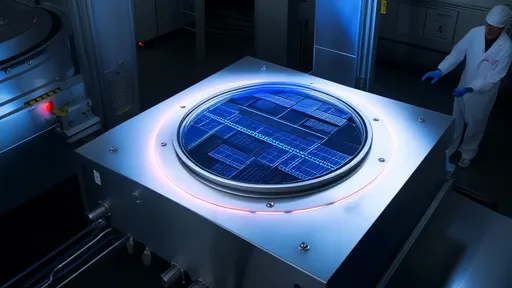

The semiconductor industry has long been driven by the relentless pursuit of higher chip yields, a metric that directly impacts profitability and supply chain efficiency. As process nodes shrink and designs grow more complex, maintaining optimal yield rates has become a formidable challenge for foundries and integrated device manufacturers alike. Yield management is no longer just a manufacturing concern—it has evolved into a strategic imperative that influences everything from product roadmaps to customer relationships.

Understanding the fundamentals of chip yield begins with recognizing its two primary components: functional yield and parametric yield. Functional yield refers to the percentage of chips that operate correctly after fabrication, while parametric yield measures how many devices meet specified performance targets. Both are critical, but their relative importance shifts depending on application. Automotive and aerospace applications, for instance, prioritize functional yield above all else, while consumer electronics may tolerate lower parametric yields if cost targets are met.

The relationship between yield and technology nodes presents a paradox that has shaped industry dynamics for decades. Conventional wisdom suggests that smaller geometries should lead to higher transistor counts and better performance at lower cost. However, the reality is far more nuanced. Each node shrink introduces new yield detractors—from increased susceptibility to defects to more complex multi-patterning requirements. This explains why many companies have adopted a more measured approach to node transitions, carefully weighing the yield trade-offs against performance benefits.

Defect reduction strategies have become increasingly sophisticated as traditional methods reach their limits. Where once simple visual inspection sufficed, today's fabs employ everything from machine learning-based pattern recognition to advanced electron microscopy. The most progressive foundries have implemented comprehensive defect prevention systems that monitor equipment health in real-time, predicting potential yield excursions before they occur. This shift from reactive to proactive yield management represents one of the most significant advancements in semiconductor manufacturing in recent years.

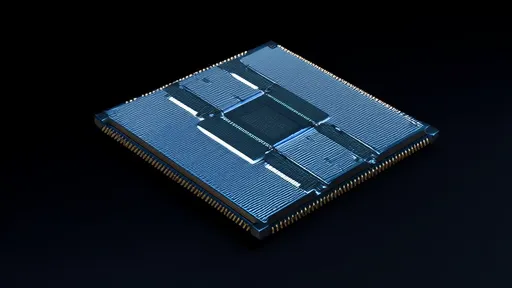

Packaging innovations are rewriting traditional yield equations. As chipmakers embrace advanced packaging technologies like chiplets and 3D stacking, the definition of yield has expanded beyond the wafer. Now, assembly and test processes contribute significantly to overall yield loss. The industry's response has been to develop new metrology tools specifically designed for package-level inspection and to create tighter integration between front-end and back-end manufacturing data systems. This holistic approach to yield optimization across the entire production flow is becoming a key differentiator for leading semiconductor companies.

The human factor in yield improvement is often underestimated but remains crucial. Despite increasing automation, experienced process engineers still play a vital role in identifying subtle yield patterns and developing innovative solutions. Many fabs have established cross-functional yield teams that bring together experts from design, process integration, and manufacturing to address complex yield issues. This collaborative approach has proven particularly effective in tackling systemic yield challenges that span multiple process steps.

Economic considerations surrounding yield have grown more complex in the current market environment. While the semiconductor industry has traditionally focused on maximizing yield percentages, some companies are now adopting more nuanced yield optimization strategies. For certain products, it may be economically advantageous to accept slightly lower yields if it means faster time-to-market or the ability to serve multiple market segments with a single design. This represents a fundamental shift in how the industry values yield—from an absolute metric to a flexible parameter that must be balanced against other business objectives.

Emerging materials present both opportunities and challenges for yield management. The introduction of new channel materials like gallium nitride and silicon carbide has enabled breakthrough performance in power electronics and RF applications. However, these materials often come with inherent yield disadvantages compared to mature silicon processes. Manufacturers are investing heavily in developing specialized processes that can deliver acceptable yields while maintaining the performance advantages of these exotic materials. The success of these efforts will largely determine how quickly new materials can achieve mainstream adoption.

The yield landscape for artificial intelligence chips differs markedly from traditional processors. AI accelerators often incorporate redundant computing elements and error correction mechanisms that make them more tolerant to certain types of defects. This architectural resilience allows designers to push the limits of process technology while maintaining acceptable yields. Some companies are even exploring intentionally imperfect manufacturing techniques that trade marginal yield improvements for significant performance gains—an approach that would be unthinkable in conventional CPU manufacturing.

Yield learning cycles have accelerated dramatically due to advances in data analytics. Where once it might take months to identify and resolve a yield issue, modern fabs can now detect patterns and implement solutions in weeks or even days. This acceleration is largely due to the implementation of comprehensive data lakes that aggregate information from thousands of sensors across the manufacturing process. Advanced correlation algorithms can pinpoint subtle relationships between seemingly unrelated process parameters and yield outcomes, enabling faster root cause analysis.

The globalization of semiconductor manufacturing has introduced new yield management complexities. As companies operate fabs in different regions and outsource various production steps, maintaining consistent yield standards across geographies has become challenging. Differences in equipment sets, local supply chains, and even environmental conditions can all impact yield. Leading companies are addressing this through centralized yield management systems that enforce uniform standards while allowing for local optimization where appropriate.

Looking ahead, the industry faces fundamental questions about the limits of yield improvement. While incremental gains will continue through better processes and equipment, some experts believe we're approaching physical limits for certain technologies. This has sparked renewed interest in alternative computing architectures that may be more tolerant to manufacturing variations. Regardless of how these trends evolve, one thing remains certain: yield will continue to be a critical factor shaping the semiconductor industry's trajectory for years to come.

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025

By /Aug 15, 2025